金属化重布线层技术:实现高密度整合与高速讯号传输的核心

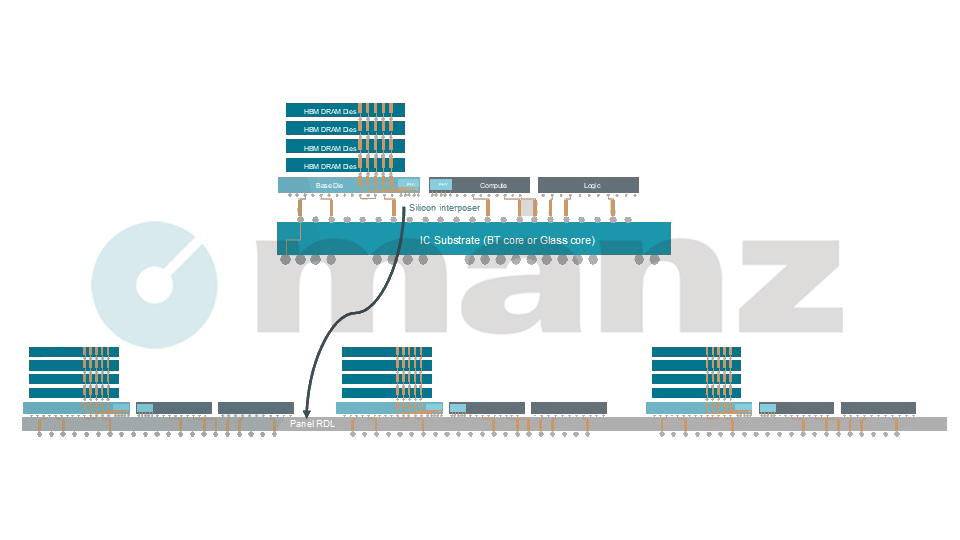

先进封装的高密度整合关键在于重布线层RDL(Redistribution Layer) 技术。作为晶片与基板之间的核心互连层,RDL不仅可重新分布晶片 I/O 接点、缩短讯号路径,提供更紧密的电气连结,并有效提升RFIC、 AI、5G、HPC 等晶片应用所需的高速、高频讯号传输效率与稳定性;更透过区域性互连,从传统 PCB 与载板制程,跃升至薄膜制程以及 2.5D、3D 等高阶高整合度的封装架构。